TSMC continue de repousser les limites de la miniaturisation avec ses nouveaux procédés de gravure en 2 nm et 1,4 nm. Ces avancées technologiques marquent un tournant majeur pour l’industrie, mais elles s’accompagnent de coûts de production sans précédent, qui pourraient rebattre les cartes sur le plan économique et concurrentiel.

Des prix qui s’envolent

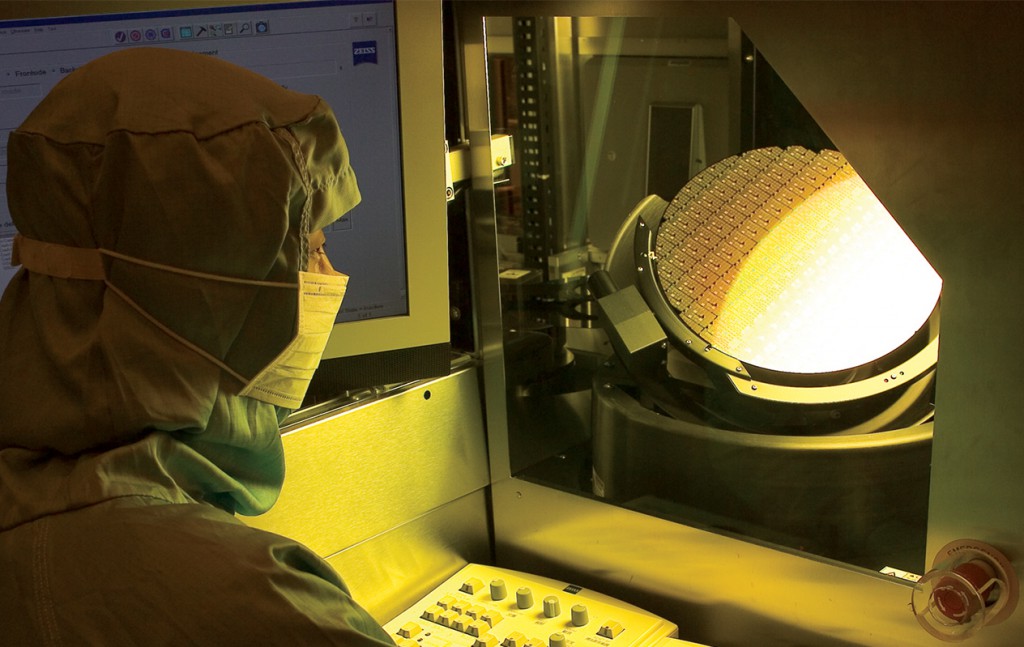

Le coût d’un wafer en 2 nm chez TSMC pourrait atteindre 30 000 dollars, soit une hausse de plus de 60 % par rapport au nœud en 3 nm. Pour les futurs wafers en 1,4 nm, les prix grimperaient jusqu’à 45 000 dollars. Cette inflation s’explique par la complexité des procédés mis en œuvre, les investissements colossaux dans les équipements de fabrication, et la baisse des rendements liée aux nouvelles structures de transistors.

À titre d’exemple, le développement d’une seule puce 2 nm pourrait exiger plus de 700 millions de dollars, tandis que la construction d’une usine compatible avec ce nœud est estimée à plus de 20 milliards de dollars.

Une adoption rapide par les leaders du secteur

Malgré ces coûts élevés, la demande pour les wafers en 2 nm reste soutenue. Apple aurait déjà réservé une part importante de la capacité pour ses prochaines générations de SoC, tandis que d’autres géants comme AMD, NVIDIA, Qualcomm ou Broadcom suivraient le même chemin.

Côté datacenter et IA, les principaux fournisseurs de services cloud – notamment Google, Microsoft et Amazon – envisagent également d’intégrer ces procédés dans leurs ASIC maison, notamment pour limiter leur dépendance aux GPU classiques.

Une transition technologique ambitieuse

Le passage au 2 nm inaugure l’adoption de la structure GAAFET (Gate-All-Around FET), censée améliorer les performances tout en réduisant la consommation énergétique. TSMC prévoit également des variantes du procédé, comme le N2P ou le N2X, avec des optimisations progressives.

Cependant, certaines fonctionnalités comme la distribution d’alimentation par l’arrière (backside power delivery) ne seront pas immédiatement disponibles et attendues dans des générations ultérieures.

Un défi industriel et économique

La montée des prix pourrait freiner l’accès aux nœuds avancés pour certains acteurs. Si les clients historiques comme Apple et les géants du cloud peuvent absorber ces hausses, d’autres entreprises pourraient être tentées d’explorer des alternatives chez Samsung ou Intel, qui travaillent aussi sur des solutions GAAFET et des procédés en dessous de 2 nm.

Malgré cela, TSMC prévoit une montée en cadence rapide, avec une capacité de 30 000 wafers 2 nm par mois attendue d’ici fin 2025. Une preuve que la transition est déjà bien engagée, même si elle ne sera pas sans conséquences sur l’équilibre global du marché.