La DDR5 :

Cela fait quelque temps déjà que Intel supporte la DDR5. Mais maintenant avec l’arrivée des nouveaux processeurs Ryzen 7000 et du socket AM5, ce format de mémoire tend à devenir timidement la prochaine norme.

Contrairement à ce que propose l’architecture Alder Lake qui dispose aussi bien d’une gestion de la DDR4, que celle de la DDR5 (4800 MT/s). AMD réalise une transition brutale avec ces nouveaux Ryzen qui sont uniquement compatibles DDR5.

La DDR5 présente plusieurs améliorations par rapport à la DDR4 et en premier lieu nous avons la fréquence. La fréquence nominale actuelle de la DDR4 se situe au niveau de 3200 MHz, initialement à 2400 MHz. Bien sûr, nous trouvons des kits de mémoire DDR4 dont la fréquence est au-dessus de 4000 MHz via l’overclocking.

La DDR5 augmente la fréquence nominale à 4800 MHz comme point de départ. Bien sûr, les marques proposent déjà des kits mémoires à 5200 MHz, voire plus.

Cependant, on peut constater que cette augmentation de la fréquence s’accompagne aussi d’un relâchement conséquent des timings. Notre kit Corsair Vengeance DDR5 6000 MHz fonctionne à 40-40-40, bien loin des timings du kit Vengeance RGB Pro SL 3200 MHz qui fonctionne à 16-20-20.

La tension nominale de la DDR5 est de 1.1 V contre 1.2 V pour la DDR4. Lorsque les barrettes mémoires DDR4 disposent d’une fréquence de 3200 MHz et plus, la tension est généralement revue à la hausse à 1.35 V XMP, voire 1.45 V sur des kits d’une fréquence supérieure à 4000 MHz.

La DDR5 utilise 1.25 V comme tension XMP de référence.

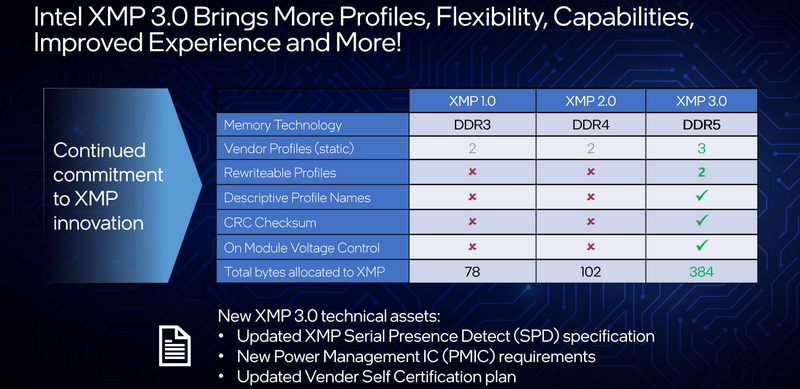

La DDR5 s’accompagne d’une nouvelle norme XMP : XMP 3.0.

La principale évolution est l’augmentation de profils XMP qui passe de 2 à 5. Trois d’entre eux sont spécifiques aux fabricants de mémoire alors que les deux autres sont des profils personnalisables.

Aussi, notre kit Corsair permet de prendre en compte ces deux profils que l’on peut paramétrer dans le bios ou à l’aide du logiciel iCUE.

En ce qui concerne la DDR5, le module DIMM dispose de deux sous-canaux 32 bits entièrement indépendants sur le même module pour une efficacité et une fiabilité améliorées contre un unique canal de 64 bits pour la DDR4.

Ceci explique le doublement de la fréquence de fonctionnement sur la DDR5.

A ce propos, nous pouvons nous poser la question de l’intérêt de continuer à mentionner la fréquence de fonctionnement en MHz (source : techsitting.com). D’ailleurs, certaines marques sont passées sur une fréquence de fonctionnement traduite en MT/s (Mega Transfers par seconde).

Cette notion existe depuis l’arrivée de la DDR qui, comme son nom l’indique (Double Data Rate), fournit le double du taux de transfert de données (MT/s) par rapport au nombre de cycles qu’il effectue (MHz).

On peut aussi lire sur le site jedec.org la notion de deux sous-canaux de 40 bits qui correspond à 32 bits + 8 bits inhérents à un module intégrant l’ECC (Error Correcting Code) (notamment des kits mémoires pour serveurs) avec code correcteur d’erreurs que l’on peut retrouver dans la mémoire DDR5.

Une valeur que l’on confronte dans ce cas, au simple canal de 72 bits de la DDR4 ECC.

La BL (Burst Lengh : quantité de données écrites par cycle) double sur chaque canal, pour passer à 16 bits (contre 8 bits pour la DDR4).

Une autre amélioration est introduite avec la technologie SBRF (Same Bank Refresh). L’actualisation automatique de la même banque de données offre de meilleures performances en permettant à certaines banques de s’actualiser pendant que d’autres sont en cours d’utilisation. Des banques qui sont par ailleurs au nombre de 32 (8 groupes de 4) contre 16 pour la DDR4 (4 groupes de 4).

Pour finir, chaque barrette à sa propre puce PMIC (Power Manager Integrated Circuit) qui est un circuit intégré de gestion de l’alimentation. Cette alimentation est donc directement gérée par le module mémoire et de ce fait, la carte mère n’est plus responsable de la régulation des tensions sur les puces mémoires comme avec la DDR4.

Que ce soit de la DDR4 ou de la DDR5, nous sommes toujours en présence d’un module DIMM composé de 288 points de contact. Seule l’encoche du détrompeur est positionnée différemment afin d’éviter toute erreur.

Pages:

1 2 3 4 5 6 7 8 9 10 11