La course à l’innovation technologique dans le domaine des processeurs ne cesse de s’intensifier, et la dernière annonce d’Intel ne fait que raviver la compétition. La sortie imminente du processeur Lunar Lake, qui sera officiellement dévoilé lors du Hot Chips 2024, a déjà suscité de vives discussions. Si ce nouveau venu n’égale pas encore les performances des Ryzen 9000 d’AMD ou du Strix Point, il révèle néanmoins une avancée stratégique majeure : une réduction significative de la latence, un élément clé pour les performances globales.

Lunar Lake : Un Focus sur l’Architecture et la Latence

Intel a profité de cette conférence pour dévoiler les détails de l’architecture de Lunar Lake, un domaine où l’entreprise est traditionnellement bien implantée. Parmi les innovations présentées, plusieurs méritent une attention particulière, notamment la réduction drastique de la latence entre les Tiles. En effet, Intel a réussi à réduire cette latence à moins de la moitié de celle mesurée sur le Ryzen 9000, plaçant ainsi AMD dans une position délicate.

L’architecture de Lunar Lake repose sur une construction modulaire à base de Tiles. La Compute Tile, véritable cœur du processeur, intègre désormais plus d’unités et adopte une structure monolithique, caractéristique des anciens Core d’Intel. Toutefois, certaines fonctions secondaires ont été déplacées vers la Platform Controller Tile, une évolution de la SoC Tile de Meteor Lake.

Une autre innovation concerne la mise en place d’un Dummy Tile, un composant conçu pour équilibrer la surface occupée par les différentes Tiles et maximiser l’efficacité du silicium disponible.

Une Réduction de Latence qui Change la Donne

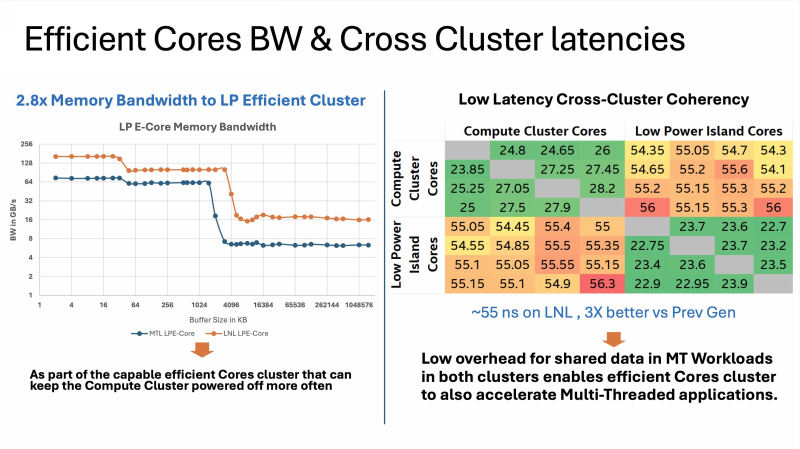

Le point fort de cette nouvelle architecture réside dans l’intégration de quatre E-Cores au sein de la Compute Tile, organisés autour d’un Network on Chip (NOC) qui optimise le cache et, par conséquent, réduit la latence. Cette approche permet également de limiter l’accès à la DRAM, ce qui se traduit par une bande passante améliorée et une consommation d’énergie réduite.

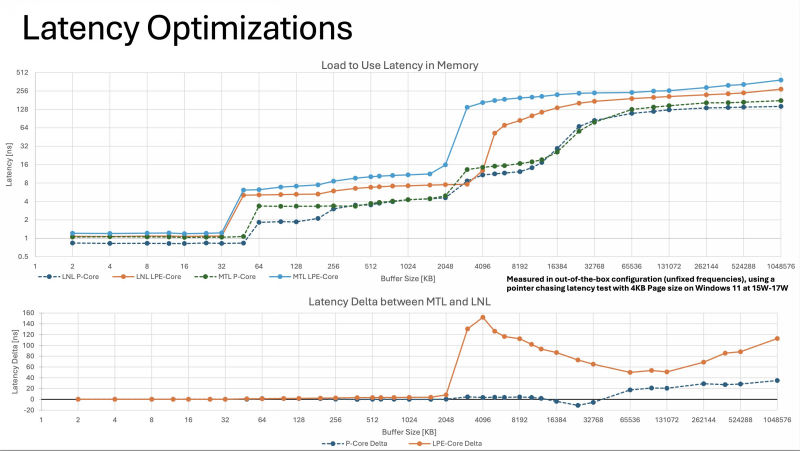

L’innovation majeure d’Intel est l’introduction d’un cache connecté horizontalement au NOC, fonctionnant de manière similaire aux TSV (Through-Silicon Vias) utilisés dans les processeurs Ryzen X3D, mais avec une approche différente. Ce cache supplémentaire, bien que de petite taille, joue un rôle crucial en interconnectant les P-Cores et E-Cores, et en maintenant une latence minimale.

Intel Devance AMD sur le Terrain de la Latence

En comparant les architectures de Lunar Lake et Zen 5, il apparaît que malgré des objectifs différents — efficacité maximale pour Intel et performances maximales pour AMD — la latence reste un facteur critique. Les données montrent que la latence moyenne entre les Tiles de Lunar Lake est d’environ 55 nanosecondes, contre 120 à 130 nanosecondes pour AMD Zen 5. Ce résultat place Intel en position de force, avec une latence réduite de moitié par rapport à AMD, et trois fois moindre que celle de Meteor Lake.

Alors qu’AMD travaille déjà sur une solution via une mise à jour du microcode AGESA, la réduction de la latence par Intel pourrait avoir un impact significatif sur les performances globales des processeurs Ryzen 9000. Ce développement marque un retournement de situation surprenant pour Intel, qui était en difficulté il y a à peine un an, et souligne la complexité et l’importance de la gestion de la latence dans les architectures modernes.

Source