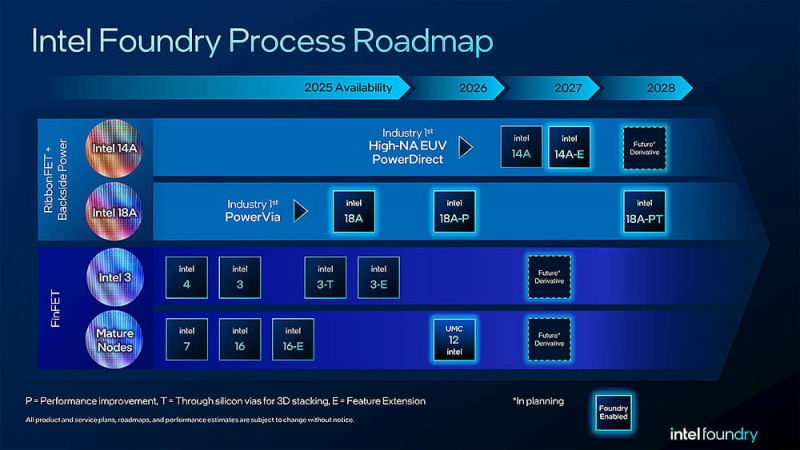

Alors qu’Intel mise tout sur sa stratégie « IDM 2.0 » et sa branche Intel Foundry pour reprendre la couronne de la gravure face à TSMC, un grain de sable vient gripper l’engrenage. Le passage à la gravure Intel 14A (équivalent au 1,4 nm), qui repose sur l’utilisation des nouvelles machines High-NA EUV d’ASML, rencontre des obstacles techniques majeurs, notamment au niveau de l’OPC (Optical Proximity Correction).

Décryptage d’un enjeu crucial pour le futur de nos processeurs.

Le High-NA EUV : L’arme fatale d’Intel en difficulté ?

Pour rappel, Intel a été le premier acteur de l’industrie à recevoir et à installer les machines de lithographie Twinscan EXE:5000 (High-NA EUV) d’ASML. Ces colosses, coûtant plus de 350 millions d’euros l’unité, sont censés permettre une résolution de gravure bien plus fine grâce à une ouverture numérique (NA) passant de 0,33 à 0,55.

L’objectif d’Intel était clair : sauter l’étape du « Double Patterning » (utilisée par TSMC) pour passer directement à une exposition simple plus précise, réduisant ainsi les coûts et les cycles de production. Cependant, la théorie se heurte aujourd’hui à la réalité de la physique optique.

Le problème de l’OPC (Optical Proximity Correction)

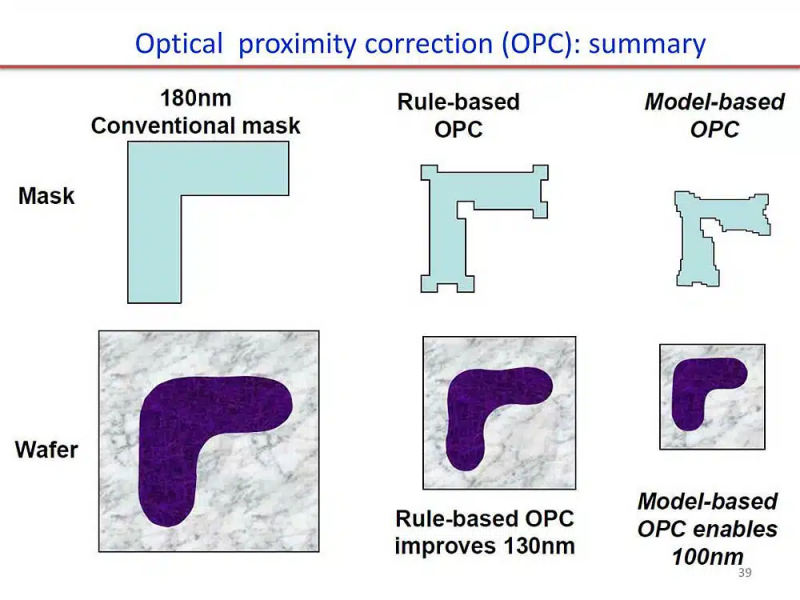

Le point de friction actuel se situe au niveau de l’OPC. Dans la lithographie moderne, les motifs dessinés sur les masques ne ressemblent pas exactement aux circuits finaux. On utilise l’OPC pour modifier les formes du masque afin de compenser les effets de diffraction de la lumière.

Avec le High-NA EUV, Intel fait face à plusieurs défis inédits :

-

L’imagerie anamorphique : Contrairement à l’EUV standard, le High-NA utilise des lentilles qui ne réduisent pas l’image de manière uniforme (facteurs de réduction différents sur l’axe X et Y).

-

Les effets d’ombre : À ces échelles, l’angle d’incidence de la lumière crée des ombres sur le masque, déformant les motifs projetés.

-

La complexité logicielle : Les algorithmes d’OPC actuels peinent à modéliser avec précision ces nouveaux paramètres, entraînant des défauts de gravure sur les premiers tests du nœud 14A.

Intel vs TSMC : Deux stratégies opposées

Cette situation met en lumière le pari risqué de Pat Gelsinger.

-

La stratégie d’Intel : Adopter le High-NA le plus tôt possible pour éviter les limites de l’EUV classique. Si Intel réussit à corriger ses problèmes d’OPC, il disposera d’une avance technologique majeure sur le 1,4 nm.

-

La stratégie de TSMC : Le géant taïwanais a choisi de pousser l’EUV standard (0,33 NA) à ses limites, quitte à multiplier les expositions (Multi-patterning). TSMC ne prévoit d’utiliser le High-NA qu’aux alentours de 2026-2027, jugeant la technologie encore trop immature et coûteuse.

Si les problèmes d’Intel persistent, le nœud 14A pourrait subir des retards ou afficher des rendements (yields) insuffisants, laissant le champ libre à TSMC et ses clients (Apple, NVIDIA, AMD).

Quelles conséquences pour les utilisateurs et le marché ?

Pour nous, passionnés de hardware et de modding, les enjeux sont concrets. Le succès du nœud Intel 14A conditionne l’efficacité énergétique et les performances des architectures post-2026.

-

Performances par Watt : Un échec ou un retard sur le 14A obligerait Intel à optimiser davantage ses nœuds existants (Intel 18A), limitant potentiellement le gain générationnel de performance.

-

Disponibilité : Si la mise au point de l’OPC sur High-NA prend plus de temps, les volumes de production seront limités au lancement.

-

Coût des composants : L’investissement massif dans le High-NA doit être rentabilisé. Si les rendements sont faibles, le prix des processeurs haut de gamme pourrait continuer de grimper.

Un saut technologique nécessaire mais périlleux

Intel n’a pas le droit à l’erreur. Le passage au High-NA EUV est l’équivalent d’un saut dans l’inconnu technologique. Les difficultés actuelles liées à l’OPC prouvent que la maîtrise de la lumière à l’échelle de l’atome est un défi constant.

Cependant, il est courant que les nouveaux procédés de gravure rencontrent des « murs » techniques en phase de développement. La capacité d’Intel à mobiliser ses ingénieurs et ses partenaires logiciels pour résoudre ces problèmes de correction optique déterminera qui, d’Intel ou de TSMC, dominera l’ère du sub-2nm.

Sources et lectures complémentaires :