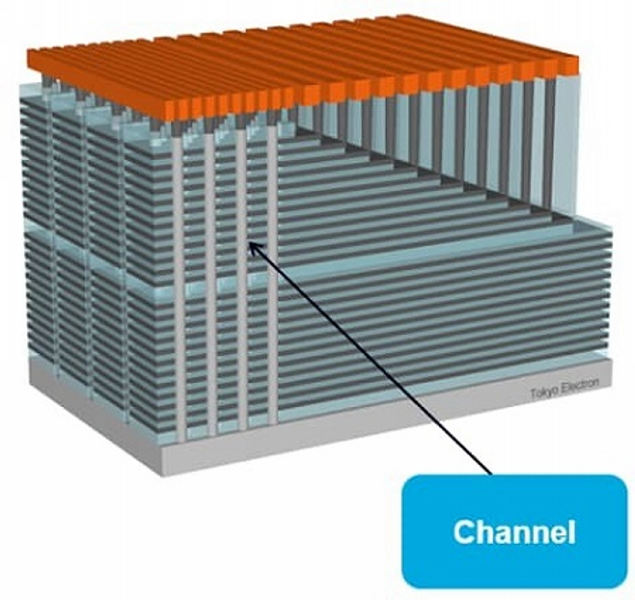

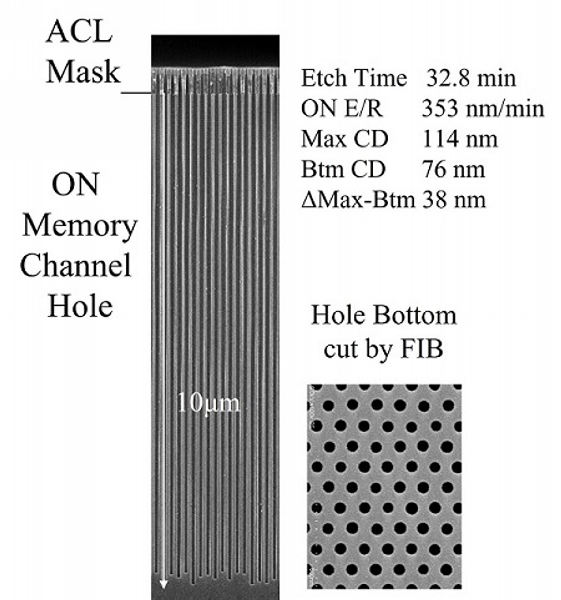

Tokyo Electron (TEL) a annoncé que sa base de développement et de fabrication de systèmes de gravure au plasma a développé une technologie innovante de gravure pour empiler des puces de mémoire flash NAND 3D avec plus de 400 couches. Le nouveau processus de l’équipe de développement utilise pour la première fois les applications de gravure diélectrique dans la plage des basses températures, ce qui donne un système avec des taux de gravure extrêmement élevés.

Cette technologie innovante peut non seulement réaliser une gravure à rapport hauteur/largeur élevé avec une profondeur de 10 microns en seulement 33 minutes, ce qui réduit le temps, mais aussi la géométrie de la structure, ce qui aide également à fabriquer de plus grande capacité pour les Puces de mémoire flash 3D NAND.

Cependant plus on ajoute de couches dans une puce mémoire et plus certains problèmes apparaissent :

- En effet, l’augmentation du nombre de couches peut augmenter la possibilité d’interférences entre elles et, par conséquent, la fiabilité lors du stockage des données.

- Du fait de l’augmentation de la longueur des vias à travers le silicium , on peut observer une augmentation de la latence, mais aussi de la consommation d’énergie.

- La gestion des cellules mémoire devient beaucoup plus complexe , rendant difficile l’accès aux informations, et la mise en place de systèmes de correction d’erreurs.

- Un nombre de couches plus élevé entraîne une diminution de la fiabilité des puces .

C’est pourquoi de nouveaux processus de fabrication doivent être créés pour permettre d’avoir des mémoires Flash NAND à 400 couches, car en utilisant les technologies actuelles, les différents points que nous avons décrits comme des problèmes peuvent apparaître. Il faudra donc attendre que la technologie progresse mais cela reste une belle prouesse et une nouvelle piste de développement.

Source